从芯片封装看导电银胶的选择:高粘接力、低电阻与高导热的技术要求

关键词: #导电银胶 #芯片封装材料 #DieAttach #高导热银胶 #体积电阻率 #离子杂质控制 #半导体封装工艺 #引线键合 #导电胶的粘接力 #SCITEO #峻茂新材料 #烧结银胶 #导电胶工艺异常

摘要:

随着半导体元器件向微型化、高功率密度方向发展,传统的连接材料焊锡膏在 0.65mm 以下节距及要求规避 230℃ 高温焊接的精密工艺中已无法满足需求。导电银胶(ECA)作为无铅化、高可靠性的互连材料被广泛应用。本文深度剖析导电银胶在半导体芯片固晶(Die Attach)、晶振、传感器件中的核心应用场景,并从底层材料物理学出发,详细拆解体积电阻率、导热率、粘接力及离子杂质四大核心参数的内在逻辑。针对客户在高速点胶及固化工艺中常见的分层、界面阻抗升高、热循环失效等高阶工艺问题,提供基于峻茂新材料(SCITEO)高可靠性导电/烧结材料体系的系统性解决方案,助力精密电子制造企业规避量产风险。

一、 导电银胶的高端精密应用场景

传统焊锡工艺的高温会损伤热敏器件,且含铅焊锡不符合环保要求。作为半导体封装产业链的一员,峻茂认为导电银胶凭借其优异的工艺适配性和性能,成为以下高精尖领域的唯一解:

1. 半导体芯片封装(Chip Packaging / Die Attach)

在引线框架(Leadframe)、QFN、BGA等IC封装制程中,固晶步骤需要将裸芯片(Die)固定在基板上。由于芯片背面通常有镀银或镀金层,导电银胶在此不仅起到机械固定作用,更承担着欧姆接触与背部散热的双重任务。尤其是功率半导体(第三代半导体SiC/GaN),对芯片背面的导热率要求极高。

2. 精密石英晶振(Crystal Oscillators)

晶振封装对于内部气氛的要求达到了苛刻的程度。导电银胶不仅需要提供导电通路,其固化后的释气率必须极低。任何挥发性有机物(VOCs)的冷凝都会附着在石英晶片上,导致晶振频率漂移或直接停振。

3. 传感器件与汽车电子(Sensors & Automotive)

汽车电子面临引擎舱内严酷的温度剧变(-40℃ 至 150℃+)。峻茂耐高温系列导电胶(Tg195℃)能够满足极端温度下的连续工作,且耐低温导电胶可对抗 -70℃ 的极寒环境。这要求胶体在宽温域下具有稳定的储能模量和低应力特性。

二、四大核心参数的底层逻辑

化学品TDS绝不是表面的数字,而是数字背后的物理与化学机制。

1. 粘接力(Adhesion Strength):抗击热机械应力

现象: 客户抱怨“导电银胶固化后,能够轻松剥离粘接面”。

底层逻辑: 粘接力不足不仅仅是你原稿中提到的“材料分层”或“银粉粘胶成分下降”。在芯片封装中,最大的杀手是热膨胀系数(CTE)失配。 芯片(硅的CTE约为3 ppm/K)与铜框架(CTE约为 17 ppm/K)之间存在巨大差异。当经历热循环时,导电胶层会承受巨大的剪切应力。如果导电胶的玻璃化转变温度(Tg)和模量设计不合理,无法吸收这种内应力,就会在界面处产生微裂纹,导致粘接失效和电阻瞬间飙升。

- 峻茂方案: 峻茂加温固化导电银胶通过高Tg(140-195℃)和低热膨胀系数(Low CTE<30)配方设计,不仅能提供极高的初始剪切强度(16MPa),更能经受严格的 JEDEC MSL(湿度敏感等级)和 TCoB(板级热循环)测试。

2. 体积电阻率(Volume Resistivity):渗流阈值

现象:客户要求电阻率越低越好。

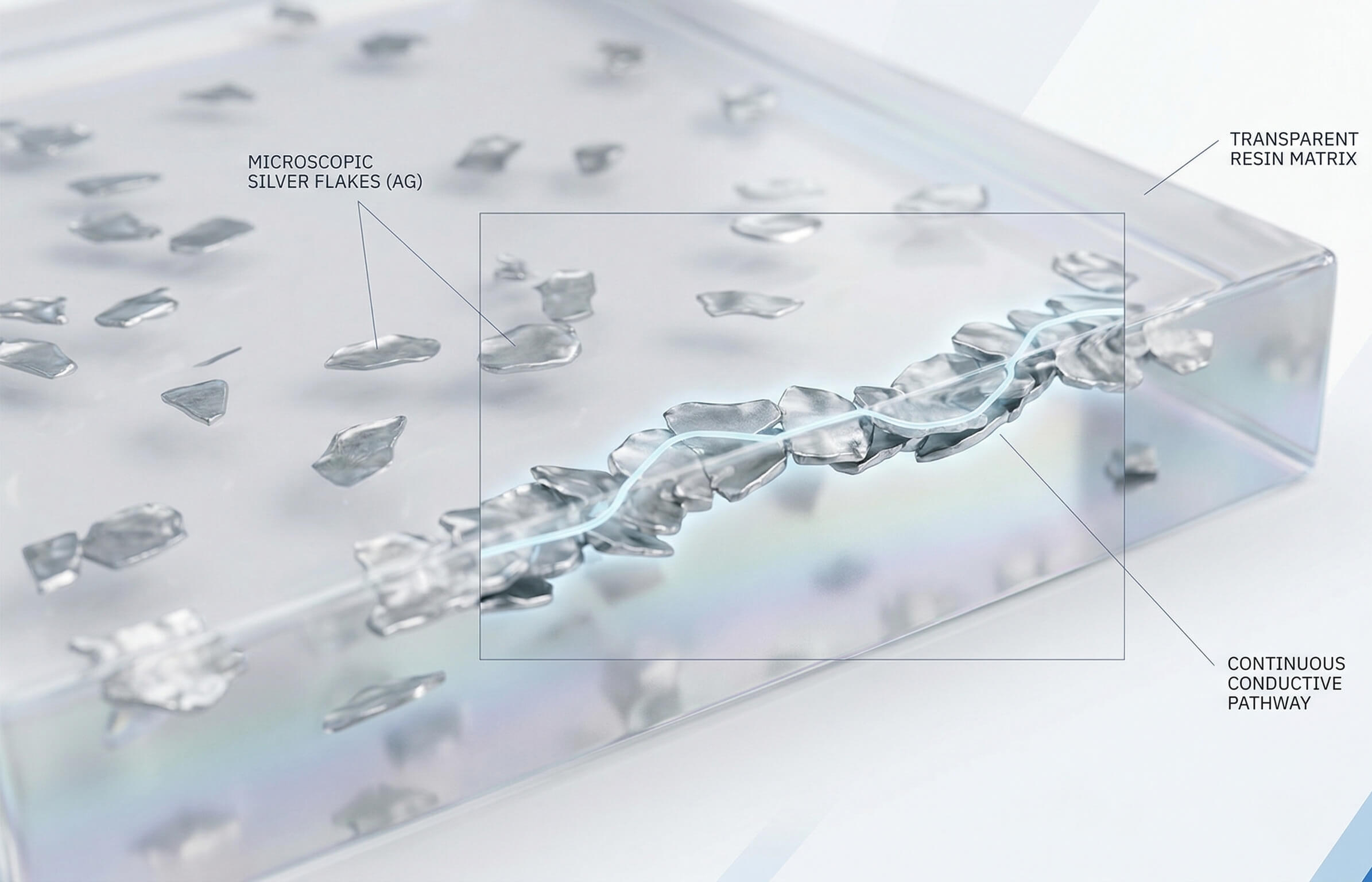

底层逻辑: 导电胶的导电机制基于渗流理论(Percolation Theory)。当银粉在树脂基体中的体积分数超过临界值时,银片相互接触形成导电网络。公式表示为 ρ = R ·A/L。

- 微米级银片(传统ECA): 靠物理接触导电,电阻率通常在 10^-4 Ω cm 级别。峻茂目前导电银胶产品最低电阻率在2×10^-5 Ω cm,若追求更低的电阻,则强行增加银粉比例,会导致树脂含量过低,大幅丧失粘接力和点胶工艺性。

- 纳米烧结银(Sintering Silver): 为了满足更高要求,峻茂产品线中具有极低电阻率(可达 2 10^-6 Ω cm量级)的系列,本质上利用了纳米银颗粒在相对低温下(表面能驱动)发生冶金熔接,彻底消除界面接触电阻,真正实现“平替主流进口同类” 的顶配性能。

3. 导热率(Thermal Conductivity):声子散射

现象: 功率器件需要极高的散热能力。

底层逻辑: 热量在聚合物体系中主要依靠晶格振动产生的声子来传递。高纯度的聚合物本身是热的不良导体,声子在“银颗粒-树脂”界面会发生强烈的散射,产生极大的界面热阻。

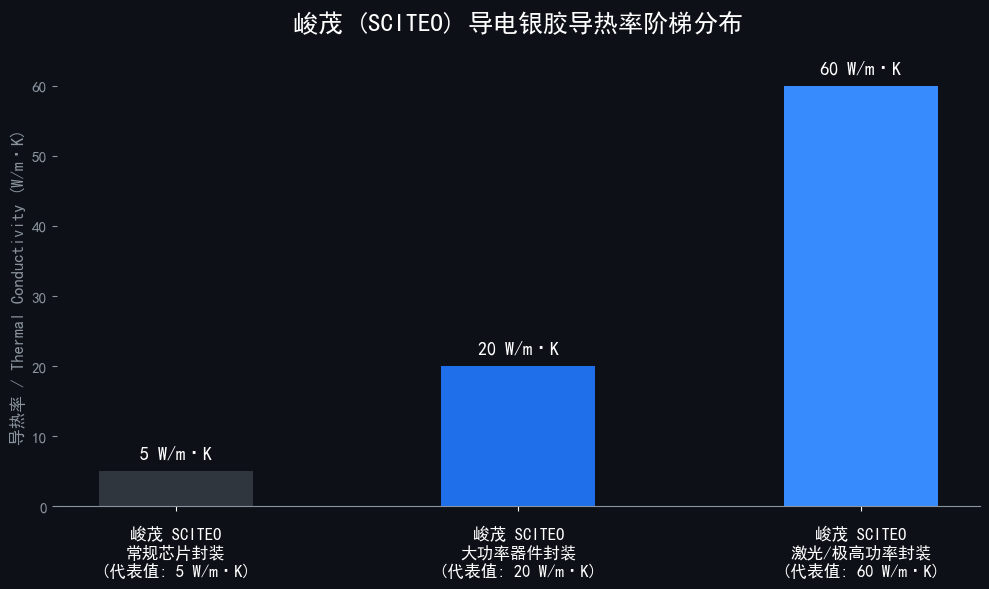

- 因此,峻茂的导热体系分为两个梯队:针对常规 LED 光电及汽车电子,提供 5-10 W/m K 的高填充改性银胶;而针对第三代半导体等大功率发热导热应用,则提供高达 20-60 W/m K 的高导热导电银胶,通过形成连续的纯银骨架,将热流通道彻底打通。至于峻茂烧结银胶可提供260 W/m K的导热系数。

4. 离子杂质(Ionic Impurities):高阶制程

现象: 客户在进行高温高湿偏压测试(THB/HAST)后,芯片发生短路或腐蚀。

底层逻辑: 这是由于导电胶中游离的氯离子(Cl^-)、钠离子(Na^+)、钾离子(K^+)在电场和水汽作用下,发生了电化学迁移,甚至引发导电阳极丝(CAF)现象。高纯度、低离子杂质不仅是为了防“分层”,更是为了防止在纳米级线宽的芯片基板上发生不可逆的电化学腐蚀。峻茂新材料选用极低离子杂质的高纯度体系,是从根本上保障电子元器件的使用寿命。

三、先进封装工艺中的问题

导电银胶因技术相对复杂,对生产工艺要求也极高,在量产中更致命的是以下高阶工艺缺陷:

1. 树脂渗出导致的打线失效

- 问题: 固晶后,导电胶中的环氧树脂成分在毛细作用或表面张力驱动下,渗出到芯片焊盘周围的镀金层上。

- 后果: 当进行后续的引线键合(Wire Bonding)时,渗出的绝缘树脂会导致金线虚焊(Non-stick on pad, NSOP)或键合拉力极度低下。

- 峻茂建议: 峻茂通过调整树脂体系的表面张力和填料润湿性,并建议客户优化基板的等离子清洗参数,从双向控制RBO现象。

2. 界面空洞与不完全固化

- 问题: X-Ray检测发现芯片底部存在大量空洞,或导电胶加温后呈现液状、不完全固化。

- 底层剖析: 空洞不仅会造成局部热点,还会应力集中导致开裂。其成因除了打胶路径闭合包气外,主要来源于回温过程中凝结的水汽 和胶体内部低分子挥发物。

- 峻茂建议: 针对水汽问题,峻茂不仅采用真空铝箔及冷藏包装,更强制要求客户:必须在室温下自然回温,严禁加热强制回温。剧烈温差导致的冷凝水不仅会引发空洞,更会破坏固化剂体系,导致固化异常。

3. 银迁移

- 问题: 在高湿及直流电场下,银离子从阳极溶解并在阴极析出,形成树枝状结晶,最终导致线路短路。

- 底层剖析: 银的电化学活性较高。针对这一难题,峻茂在特定高可靠性型号中引入了特殊的防迁移抑制剂或采用包覆技术,大幅提升了抗偏压高湿测试的能力。

四、 结语

导电银胶从来不是简单的“胶水加上银粉”,它是高分子物理、流变学与粉体冶金科学的复杂交汇点。从芯片制程到精密电子,每一次连接都关乎终端产品的生命周期。峻茂新材料(SCITEO)依托众多半导体封装客户的应用经验,为客户提供从室温自干到超高温(>500℃)应用和低温固化、从常规导电到高导热和极低电阻烧结全系列的解决方案。我们不仅提供材料,更输出从点胶、固化到可靠性测试的全链路工艺护航。选择峻茂,即是选择材料科学的确定性。

附录:研发工艺工程用胶问题解答 (Technical FAQ)

Q1:峻茂的加温固化导电银胶相比双组分室温固化有什么核心优势?

峻茂回答: 双组分室温固化胶自干时间极长(通常 > 24小时),且存在体积电阻率不稳定的问题,极不适合要求高UPH的精密电子产线,双组份在CTE和离子控制劣势明显。峻茂单组分加温固化导电银胶能够提供极其优异的粘接附着力,且固化后材料的Tg和耐温范围能完美匹配元器件的应用需求,是规模化量产的优选。

Q2:对于热敏元器件,有无低温快速固化的导电胶方案?

峻茂回答: 峻茂拥有针对热敏元器件开发的低温固化(60-80℃)导电银胶。该方案能够在不损伤精密电子组件(如某些特定薄膜电容或柔性基板)的前提下,实现优异的导电匹配与机械粘接,同时为了适应大批量生产,还开发了匹配的印刷型导电胶以降低客户使用成本。

Q3:导电银胶在冰箱冷冻储存取出后,可以直接使用吗?

峻茂回答: 绝对不可以。 这是导致固化异常和空洞的最常见工艺违规。冷藏取出的导电银胶必须在室温下自然回温(通常需要2-4小时,视包装容量而定)。不可使用任何加热设备回温,否则剧烈温差会导致环境水汽大量凝结渗入胶液,严重破坏固化网络和导电网络。

-

2026-03-15

低温固化胶水怎么选?热敏元器件与红外传感芯片封装用胶白皮书

55℃ 极低温固化与 >18MPa 剪切强度:峻茂单组份环氧树脂胶技术指南

查看详情 >

-

2026-03-15

高密度 PCBA 与电子密封胶怎么选?SiP 封装与微秒级喷射点胶选择指南

挑战 <0.06% 极低收缩与不可逆防抄板保护:峻茂全谱系电子胶水技术解析

查看详情 >

-

2026-03-21

从芯片封装看导电银胶的选择:高粘接力、低电阻与高导热的技术要求

峻茂分析引线键合打线、空洞和银迁移的生产工艺问题

查看详情 >

-

2026-03-21

从晶圆3nm前道到CoWoS先进封装芯片热应力与工艺缺陷问题白皮书

峻茂深度解析GAAFET、混合键合及千瓦级算力芯片的耐温导热粘接胶

查看详情 >